# **SIG60 Reference Design**

## For New designs please refer to SIG100 new IC

#### 1. GENERAL

This reference design provides the basic circuitry for the SIG60 IC operation in a network communicating over DC power line. Multiple SIG60 boards can communicate over DC power line using the UART interface.

The SIG60 Micro module operates as a DC powerline transceiver. Only Data-In, Data-out and Ground wires are required for default operation. The SIG60 transfers any number of bytes over the powerline to all other SIG60 devices on that line..

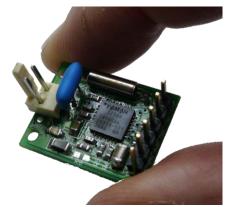

Figure 1.1 - Assembled reference SIG60 design

## 2. SIG60 Reference Design Description

#### 2.1. Demo Micro board

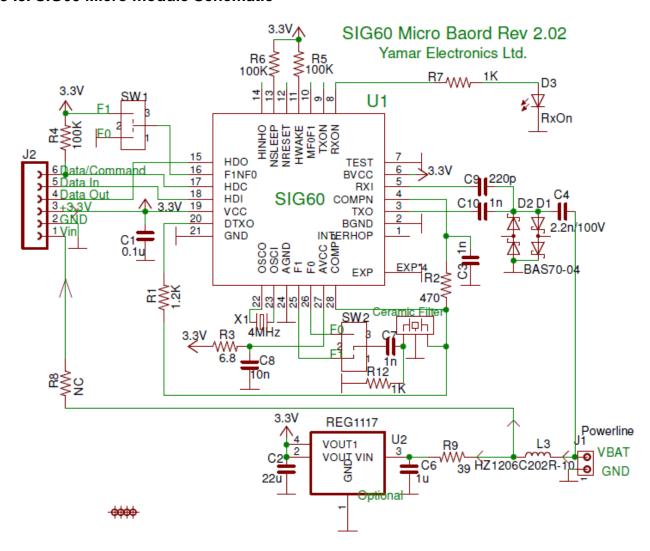

. The Micro module contains the required hardware for the SIG60 operation on a single 6.5MHz channel, the 4MHz crystal, line protection network, 6.5MHz ceramic filter, 5V-12V DC linear power supply for the 3.3V required for the device operation.

The SIG60 operates as a UART transceiver, using its HDI input and HDO output pins. Lowering the HDC pin allows access to the SIG60 internal registers. See SIG60 data sheet for detailed information. The default bit rate of the device is 19.2Kbps. The Micro module interfaces directly with any host Micro controller with a UART port via the J2 6 pins header. The connection to the powerline is via J1 connector.

## 2 .2. Signals

The received modulated signal from the DC line passes through a protection network into the RxIn input pin to an Rx amplifier inside the SIG60. The amplified signal passes via F1B pin to 6.5MHz external ceramic filter and back into RxP input. The SIG60 decodes the data and output the decoded UART data to HDO pin as an asynchronous bit stream.

On the transmitter side, the host Micro controller transfers UART data to the SIG60 via HDI pin. The asynchronous data, this data is protected by the Sig60 against errors and modulated. The DTXO pin

outputs the digitally modulated signal to the ceramic filter for shaping via R1. The shaped signal enters back into the SIG60 via F1B pin to an output amplifier. The modulated data on TxO pin drives the DC line via the protection network.

## 2.3. Hardware

The Micro module contains:

- SIG60 DC Power Line Communication device

- UART serial header

- 6.5MHz ceramic filter

- 4MHz crystal

- 6V to 12V Linear power supply

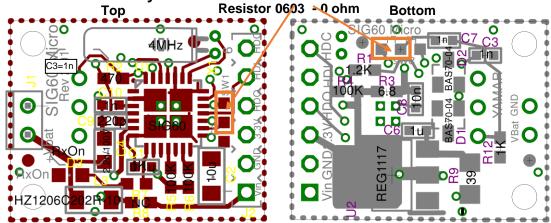

- Small size PCB (2,4x1.8 cm)

#### Connectors:

J2 - Host interface.

J1 - DC line connector.

## 3. Operation

## 3 .1. Configuration

The SIG60 mode of operation and its settings are configured at power-up, reset and whenever the Host writes into its internal register. Refer to SIG60 data sheet for further configuration information.

#### 3.2. Connectors

#### 3.2.1. JP1 - Host Interface Connector

| Pin Name                  | Direction | Pin # |

|---------------------------|-----------|-------|

| Vin (Vbat after inductor) | 0         | 1     |

| Ground                    | Р         | 2     |

| 3.3V                      | I         | 3     |

| HDO (data out)            | 0         | 4     |

| HDI (data in)             | I         | 5     |

| HDC                       | I         | 6     |

| Ground                    | Р         | 13    |

All input and output signals are compatible with 3.3V CMOS logic.

#### 3.2.2. JP2 - DC Power Line and test points

| Name               | Pin# |

|--------------------|------|

| GND                | 1    |

| VBat DC line input | 2    |

VBat input connects the module to the DC power line for communication and power supply. Power supply requirements: 6V to 12V, 80mA.

©2014-19 YAMAR Electronics Ltd. Tel: 972-3-5445294 Fax: 972-3-5445279

#### 3.3. Interfacing

The SIG60 module interfaces directly to any controller with UART port. Three signals are essential for proper operation; HDI, HDO and GND (Data In, Data Out and Ground). The use of HDC pin is required only if the device should be used in different bit rate or mode of operation.

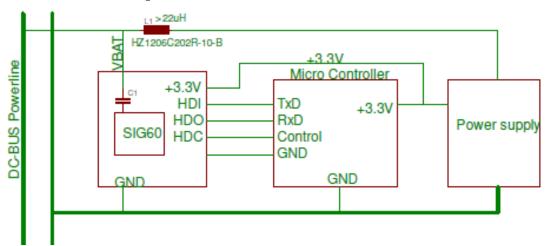

The Figure below is an example for an interface. It is recommended to add an inductor of at least 22uH (or low frequency ferrite bead with high impedance at 6.5MHz) between the SIG60 evaluation board and the Micro controller (uC) supply line to avoid possibility that the uC power supply filtering capacitor will short the SIG60 carrier signal.

Figure 3.1 - SIG60 Module Interface with a Host.

## 3 .4. Operation

- 1. Connect the communication signals via JP2 to the host uC.

- 2. Connect the Micro module to the DC Power line.

- 3. When using the default values (6.5MHz, 19.2Kbps) there is no need for any configuration. Changing the SIG60 default values is possible by lower the HDC input pin and writing to the SIG60's registers the new bit rate and mode of operation as described in the SIG60's datasheet.

- 4. Raise the HDC input and start UART communication.

- Transmit and receive UART data bytes to and from remote host over the DC power line.

©2014-19 YAMAR Electronics Ltd. AN-SIG60 Reference Design 2.02 - 3 -Tel: 972-3-5445294 Fax: 972-3-5445279

## 3 .5. SIG60 Micro module Schematic

Figure 3.2 - SIG60 Reference Schematic

## 3 .6. Micro module layout

Figure 3.2 - Module Layout